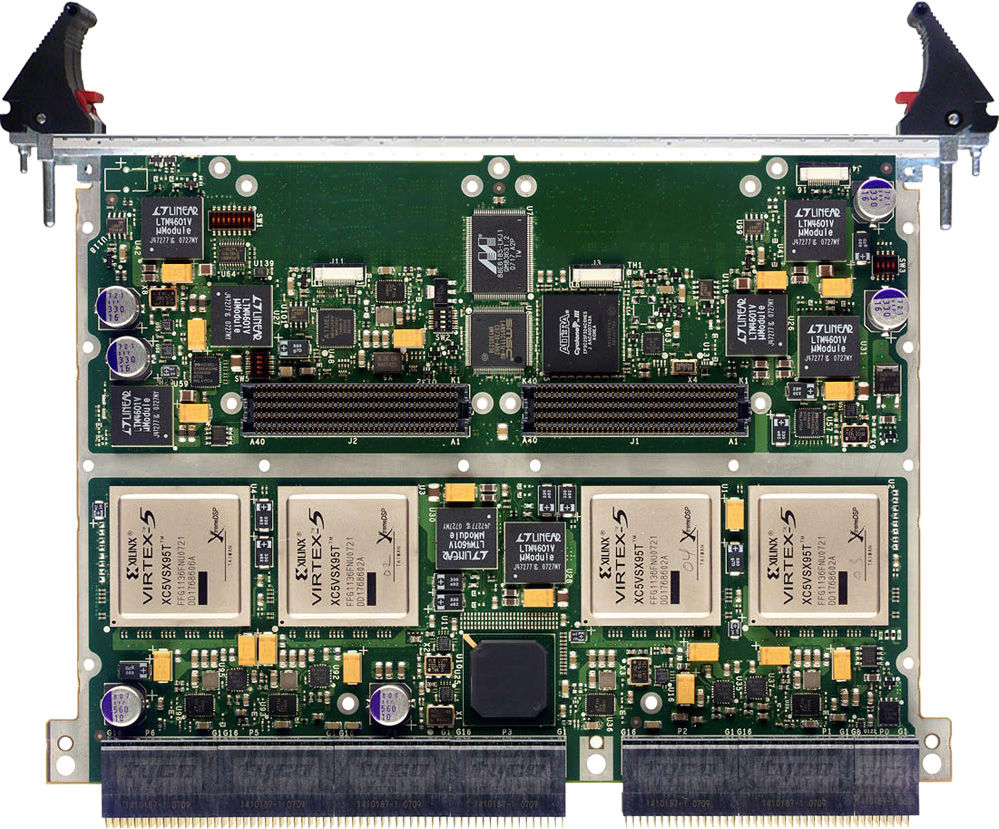

FPE650 6U VPX Quad Virtex-5

FPGAモジュール / OpenVPX

・x4 Xilinx Virtex-5 FPGAs (SX95T) ・Dual FPGA mezzanine card (FMC/VITA 57) sites ・Multiple banks of FPGA connected QDR SRAM and DDR SDRAM memory ・6U VPX form factor ・FusionXF FPGA Design Kit

FMC223

FPGAモジュール / FMC

・FPGA Mezzanine Card (FMC) per VITA-57 ・Single width ・Single DAC 14-bit at 2.5 GSPS ・2Vpp Differential Analog Output Swing ・Programmable DSP Clock ・Multi I/O LVDS input for Trig input, user defined, clock input, etc.

AMC532

FPGAモジュール / AdvancedMC

・AMC FPGA based on Altera Stratix-V (5SGXEA) in F1932 package ・Single module, mid-size or full-size ・VITA 57.1 FMC HPC Connector (compatible with LPC) ・All FMC LA, HA, HB pairs routed bi-directionally

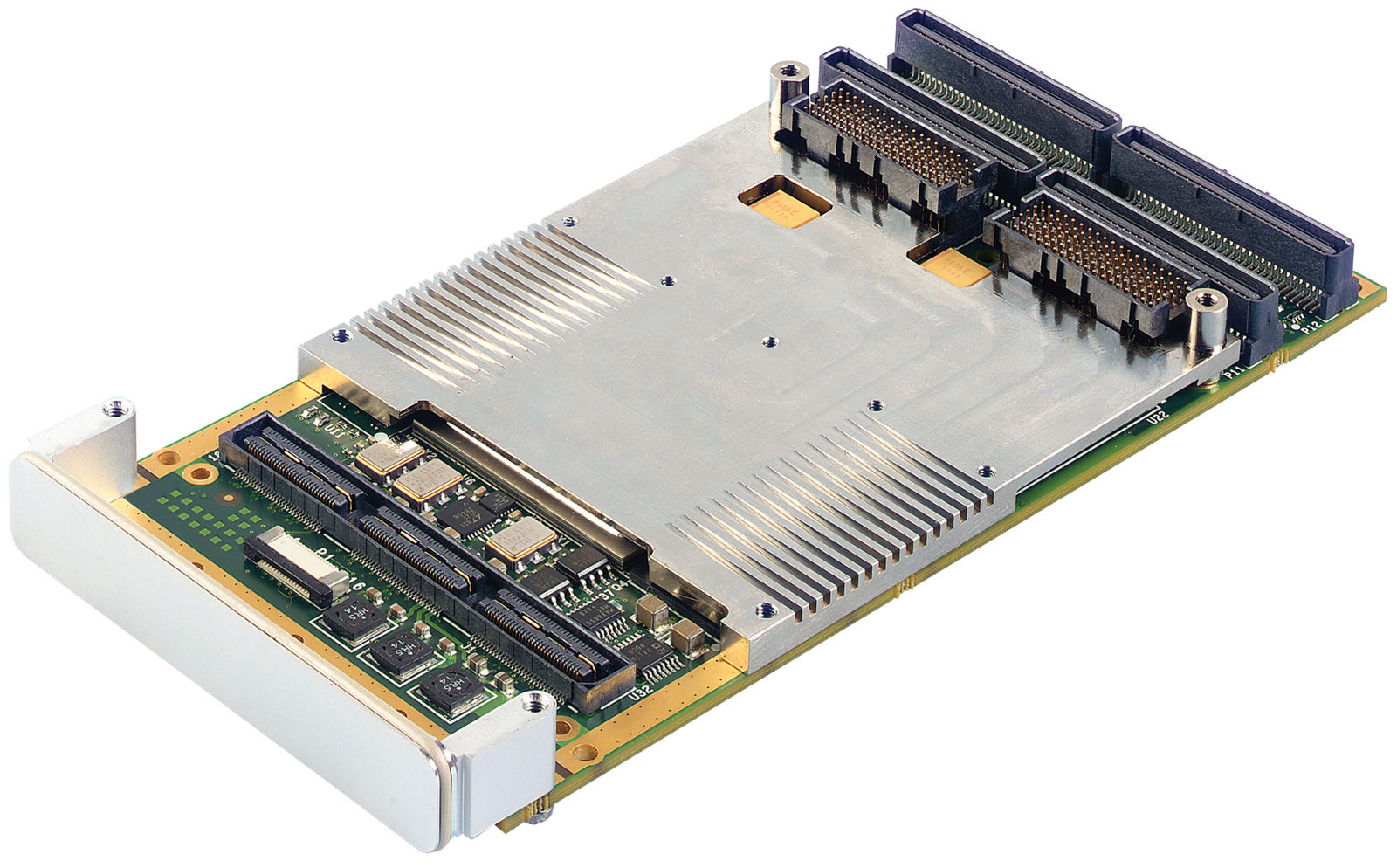

XMC-FPGA05D Virtex-5 XMC/PMC

FPGAモジュール / PMC/XMC

・Xilinx Virtex-5 SX95T (default) FPGA ・Customizable digital I/O ・Two banks of 9MB QDR2 SRAM for DSP ・Two banks of 128MB DDR2 SDRAM for large buffers ・PCIe/PCI-X interface ・Windows, VxWorks and Linux support ・FusionXF FPGA Design Kit support ・Air and Conduction cooled variants

AMC517

FPGAモジュール / AdvancedMC

・AMC FPGA carrier for FMC per VITA-57 ・Xilinx Kintex-7 410T FPGA ・AMC Ports 4-7 and 8-11 are routed to FPGA per AMC.1, AMC.2 and AMC.4 ・Option for on-board Freescale QorIQ PPC2040 with DDR3 ・FPGA can load via FLASH or via the P2040 ・On-board clock and jitter cleaner ・FPGA FLASH can be programmed ・Serial over LAN (SOL) with hardware RNG

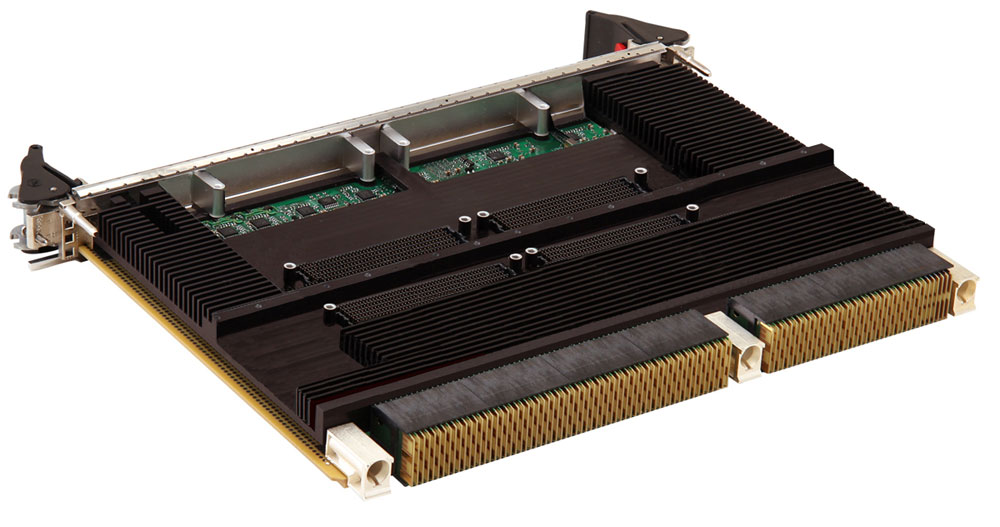

CHAMP-WB 6U OpenVPX Virtex-7

FPGAモジュール / OpenVPX

・OpenVPX™ (VITA 65) profile MOD6-PAY-4F1Q2U2T-12.2.1-11, VPX REDI (VITA 48 option) ・Single user-programmable Xilinx Virtex-7 FPGAs (X690T or X980T), with ・8 GB DDR3L SDRAM in two banks ・Four 4-lane serial data plane links to the backplane (support up to 10.3 Gbps data rates) ・Gen2 SRIO or alternate fabrics with different FPGA cores ・One 4-…

TS-PCI A40

FPGAモジュール /

・Altera EP1S40 C5 FPGA on the PCI Board and Expansion Module(s) ・8 MB of SRAM and 384 MB of SDRAM on A40 FPGA Expansion Modules ・4 MB SRAM and 1 Gigabyte SDRAM on the A40 PCI base board ・TS-PCI A40 FPGA processor delivers many times the processing of CPU or DSP boards

RAF-EC-2P

FPGAモジュール / その他の規格

・Four bi-directional avionics level discretes ・Two input and output triggers per channel - Berkeley packet filter engine - Integrated log file format - AFDX/ARINC 664 API - XML configuration format ・Advanced Software Support - Flexible packet capture API - Link level error detection - DMA transfer to host - Full throughput capability - Fle…

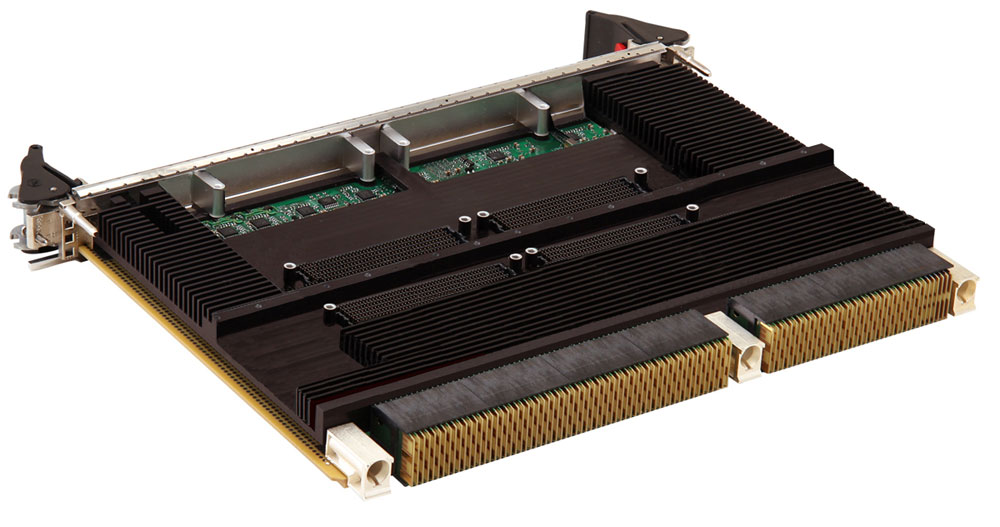

CHAMP-WB 6U OpenVPX Virtex-7

FPGAモジュール / OpenVPX

・OpenVPX™ (VITA 65) profile MOD6-PAY-4F1Q2U2T-12.2.1-11, VPX REDI (VITA 48 option) ・Single user-programmable Xilinx Virtex-7 FPGAs (X690T or X980T), with ・8 GB DDR3L SDRAM in two banks ・Four 4-lane serial data plane links to the backplane (support up to 10.3 Gbps data rates) ・Gen2 SRIO or alternate fabrics with different FPGA cores ・One 4-…

FMC210

FPGAモジュール / FMC

・FPGA Mezzanine Card (FMC) per VITA-57 ・Single width - Reference clock - Trig in/out - General purpose I/O ・Super low phase noise RF PLL Synthesizer ・RoHS compliant ・Single ADC @2.5 GSPS ・5 GHz Full Power Input Bandwidth (-3dB) ・True single core architecture (no calibration required) ・External Interleaving: - Gain Adjust - Offset Adjust - Sam…