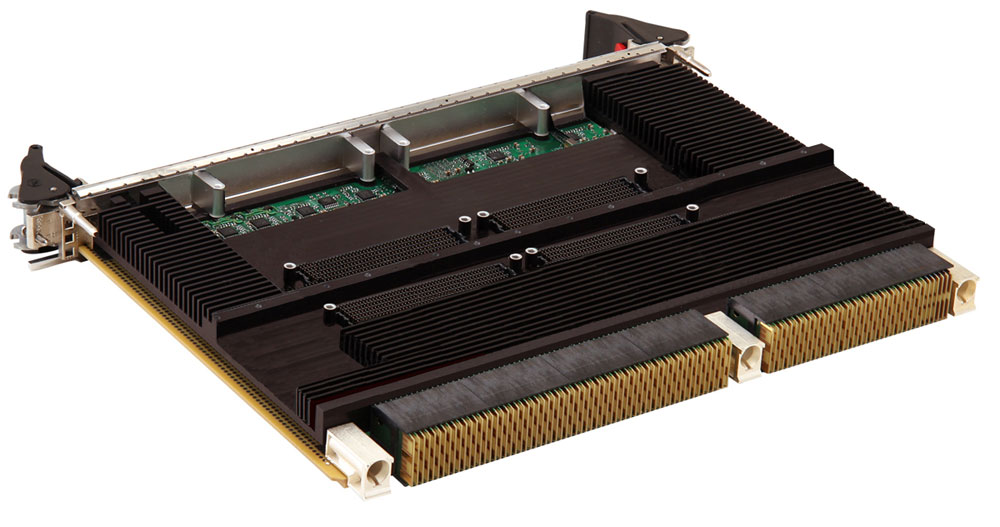

・OpenVPX™ (VITA 65) profile MOD6-PAY-4F1Q2U2T-12.2.1-11, VPX REDI (VITA 48 option)

・Single user-programmable Xilinx Virtex-7 FPGAs (X690T or X980T), with

・8 GB DDR3L SDRAM in two banks

・Four 4-lane serial data plane links to the backplane (support up to 10.3 Gbps data rates)

・Gen2 SRIO or alternate fabrics with different FPGA cores

・One 4-lane Gen3 PCIe connection to a Gen3 PCIe switch

・One additional x4 10.3 Gbps link to the backplane

・16 LVDS pairs to the backplane

・Two enhanced FMC interfaces with 128+ differential signal pairs

・One site supports JESD204B or Serial FMCs with up to 8 serial links

・The other site has optional support for up to 160 LVDS pairs with X690T FPGA

・Two Mezzanine sites with support for FMC (VITA 57) or enhanced FMC

・Onboard PCIe Gen3 switch - Two 8-lane expansion plane fabric ports to the backplane with configurable NTB support

・Sensors for monitoring board power consumption

・Support for ChipScope Pro and JTAG processor debug interfaces

・Backplane clock/sync paths to mezzanines sites

・FXTools BSP and FPGA design kit with highly-optimized IP Blocks, development environment, reference designs, scriptable simulation test benches and software libraries VxWorks and Linux variants available

・VITA 48 1” pitch format

・Ruggedization levels

・Air-cooled Level 0 (commercial)

・Conduction-cooled Level 200 (future)

・Path to variant with Processor (contact factory)

・Single user-programmable Xilinx Virtex-7 FPGAs (X690T or X980T), with

・8 GB DDR3L SDRAM in two banks

・Four 4-lane serial data plane links to the backplane (support up to 10.3 Gbps data rates)

・Gen2 SRIO or alternate fabrics with different FPGA cores

・One 4-lane Gen3 PCIe connection to a Gen3 PCIe switch

・One additional x4 10.3 Gbps link to the backplane

・16 LVDS pairs to the backplane

・Two enhanced FMC interfaces with 128+ differential signal pairs

・One site supports JESD204B or Serial FMCs with up to 8 serial links

・The other site has optional support for up to 160 LVDS pairs with X690T FPGA

・Two Mezzanine sites with support for FMC (VITA 57) or enhanced FMC

・Onboard PCIe Gen3 switch - Two 8-lane expansion plane fabric ports to the backplane with configurable NTB support

・Sensors for monitoring board power consumption

・Support for ChipScope Pro and JTAG processor debug interfaces

・Backplane clock/sync paths to mezzanines sites

・FXTools BSP and FPGA design kit with highly-optimized IP Blocks, development environment, reference designs, scriptable simulation test benches and software libraries VxWorks and Linux variants available

・VITA 48 1” pitch format

・Ruggedization levels

・Air-cooled Level 0 (commercial)

・Conduction-cooled Level 200 (future)

・Path to variant with Processor (contact factory)