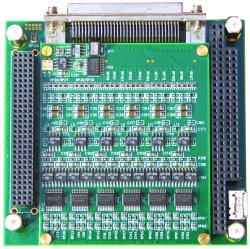

Analog Inputs:

Four Differential Sigma-Delta Analog Inputs with Dedicated 16-Bit ADC per Channel

Simultaneous Sigma-Delta Sampling of all Inputs to 1.0 MSPS per channel

Sigma-Delta A/D Architecture; Minimal or no antialiasing requirements

Analog Outputs:

4 Single-Ended Analog Outputs with Dedicated 16-Bit DAC per Channel

Simultaneous Output Clocking Rates from 30 KSPS to to 1.0 MSPS per Channel

Selectable Direct-Write or FIFO-Buffered Access

Buffer Configurable as Open for Data Streaming, or Circular for Periodic Functions

Four Differential Sigma-Delta Analog Inputs with Dedicated 16-Bit ADC per Channel

Simultaneous Sigma-Delta Sampling of all Inputs to 1.0 MSPS per channel

Sigma-Delta A/D Architecture; Minimal or no antialiasing requirements

Analog Outputs:

4 Single-Ended Analog Outputs with Dedicated 16-Bit DAC per Channel

Simultaneous Output Clocking Rates from 30 KSPS to to 1.0 MSPS per Channel

Selectable Direct-Write or FIFO-Buffered Access

Buffer Configurable as Open for Data Streaming, or Circular for Periodic Functions